2019. 4. 18. 22:53ㆍMajor/2019

1장

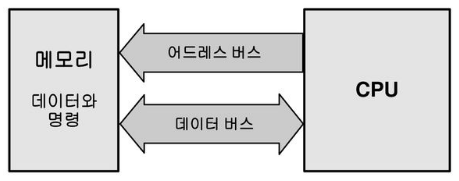

폰 노이만 구조

데이터 영역과 프로그램 영역의 물리적인 구분이 없고 버스 크기도 동일하다.

데이터와 프로그램 코드를 동일하게 취급하므로 데이터도 프로그램 코드에 함께 들어간다.

마이크로프로세서 속도가 빠를수록 고성능이다.

ex) 데스크톱 PC

하버드 구조

데이터 영역과 프로그램 영역이 물리적으로 구분되어 있고 각 버스의 크기도 다를 수 있다.

데이터와 명령어를 분리해서 처리한다.

ex) 8051, PIC, AVR

시스크(CISC)

'복합 명령어 셋 컴퓨터'

CISC 방식은 CPU가 처리할 수 있는 명령어를 모두 내장하므로 CPU 구조가 아주 복잡해진다는 특징이 있다.

CISC 방식의 장점은 뛰어난 호환성이다.

하드웨어 호환성이 좋아 하드웨어 가격이 저렴함.

리스크(RISC)

'축소 명령어 셋 컴퓨터'

RISC는 CPU에 내장된 사용 명령어를 줄여 처리 속도를 좀 더 빠르게 만든 것이 특징이다.

전체 처리 과정이 단순하여 CPU 구조가 단순해지며, 처리 속도가 더 빠른 CPU를 만들 수 있다.

x86 계열 CPU를 지원하는 프로그램을 사용할 수 없을 뿐만 아니라 하드웨어 호환성도 극히 낮다.

2장

8051 핀 구조와 기능

◼︎ 포트 0(P0) (핀 번호 : 32~39)

◼︎ 포트 1(P1) (핀 번호 : 1~8)

◼︎ 포트 2(P2) (핀 번호 : 21~28)

◼︎ 포트 3(P3) (핀 번호 : 10~17)

◼︎ 시스템 리셋(RST) (핀 번호 : 9)

◼︎ 클록 오실레이터(XTAL2, XTAL1) (핀 번호 :18, 19)

◼︎ PSEN (핀 번호 : 29)

◼︎ ALE/PROG (핀 번호 : 30)

◼︎ EA/Vpp (핀 번호 : 31)

◼︎ Vss (핀 번호 : 20), Vcc (핀 번호 : 40)

CY : 덧셈이나 뺄센 연산 시 8번째 비트에서 자리올림이나 자리내림이 발생하면 1로 세트되는 캐리 플래그다. 또한 로테이트나 부울 명령ㅇ에서 누산기로 동작 한다.

AC : 덧셈/뺄셈 연산 시 3번째 비트에서 자리올림이나 자리내림이 발생하면 1로 세트되는 보조 캐리 플래그다.

F0 : 범용 플래그로, 사용자가 정의해서 사용한다.

RS1 : 레지스터 뱅크를 선택할 때 사용한다.

RS0 : 레지스터 뱅크를 선택할 때 사용한다.

5장